JK Flip Flop wordt beschouwd als een universele programmeerbare flipflop. Waarom wordt het beschouwd als een universele flipflop?

JK flipflop heeft verschillende ingangen: J, K, S en R die gebruikt kunnen worden zoals elk ander type flip flop. De JK flipflop is in principe de verbeterde versie van de R-S flipflop, maar de uitvoer blijft hetzelfde wanneer de J- en K-ingangen LAAG zijn.

Het R-S flipflop circuit heeft misschien veel voordelen en functies in logische circuits, maar het heeft twee grote problemen:

- Set = Reset = 0 (S = R = 0) en Set = Reset = 1 (S = R = 1) moeten worden vermeden

- Als de SET- of RESET-ingangen de logische status wijzigen wanneer de klok (CLK) actief HOOG is, vindt de juiste vergrendelingsactie mogelijk niet plaats.

Om deze grote problemen op te lossen, werd de JK flipflop geconstrueerd.

We kunnen zeggen dat de JK flipflop de meest veelzijdige flipflop is, omdat deze inputs heeft zoals de D flipflop met klok input. Deze flipflop gebruikt twee inputs gelabeld met J en K.

Als de J en K input verschillend zijn, zal de output Q de waarde J hebben bij de volgende klokrand cyclus. J en K worden gebruikt om Jack Kilby te eren als de uitvinder van dit type flip flop.

We moeten eerst begrijpen hoe de JK flipflop werkt voordat we meer leren over een Master Slave JK flipflop waarheidstabel.

Wat is JK Flip Flop?

Deze basis JK flipflop is de meest gebruikte van alle flipflop circuits en staat bekend als een universele flip flop. De ingangen van deze flipflop zijn gelabeld met “J” en “K”, net zoals “S” voor SET en “R” voor RESET in S-R flipflop.

De J en K staan voor Jack Kilby als uitvinder van dit type flip flop.

De sequentiële logische werking van deze JK flipflop is hetzelfde als de R-S flipflop met dezelfde SET en RESET logische ingangen. Het enige verschil is dat de JK flipflop geen verboden invoer combinatie heeft.

JK flipflop of kortweg JK-FF, is in principe een verbeterde R-S flipflop. Deze flipflop is een combinatie van een gated R-S flipflop en een geklokte signaalang.

De klokingang voorkomt de ongeldige of illegale invoer bewerking wanneer zowel S als R gelijk zijn aan logische “1”.

Met behulp van deze geklokte invoer produceert de JK-flipflop vier verschillende invoer combinaties:

- Logica “1”

- Logica “0”

- Geen verandering

- Toggle.

Er zijn twee reacties op JK flipflop:

- Wanneer de J- en J-ingangen beide in een lage toestand zijn (logische “0”) = vindt er geen verandering plaats

- Wanneer de J- en K-ingangen beide in een hoge toestand zijn (logische “1”) aan de klokrand = verandert de uitvoer van de ene logische toestand naar de andere (“0” naar “1” en vice versa)

Deze JK flipflop kan precies als een R-S flipflop fungeren, terwijl de dubbelzinnige omstandigheden worden geëlimineerd.

Niet alleen dat, maar deze flipflop kan ook een T flip flop imiteren om de output flip flop te doen als we de J en K inputs aan elkaar koppelen.

Deze toggle applicatie kan worden gebruikt voor uitgebreide binaire tellers.

De JK flipflop heeft dezelfde functie als de R-S flipflop, maar voor een van de responsen in de waarheidstabel.

Het nadeel van de R-S flipflop zijn de verboden input combinaties hieronder:

- De ingangen S = R = 1 (actieve HOGE logische ingangen)

- De ingangen S = R = 0 (actieve LAGE logische ingangen)

Dit nadeel van de R-S flipflop wordt overwonnen door de JK flipflop in het geval:

- Actieve HOGE ingangen, de uitgang van de flipflop-schakelaar, dus verandert deze naar de andere logische toestand (voor J = K = 1)

- Actieve LAGE ingangen, de uitgang van de flipflop-schakelaar, dus verandert deze naar de andere logische toestand (voor J = K = 1)

JK flipflop actieve hoge ingangen

JK flipflop actieve lage ingangen

De bovenstaande figuren geven het circuit symbool weer van een niveau-getriggerde JK-flipflop met respectievelijk actieve HIGH- en LOW-ingangen, samen met de waarheidstabel.

Weergave van de JK-flipflop met behulp van een R-S-flipflop

De afbeelding hierboven toont ons de JK-flipflop van de R-S-flipflop met extra logische poorten.

De waarheidstabellen van JK flipflop en de Karnaugh map-oplossingen

De tabellen hierboven tonen ons de waarheidstabellen van JK flipflop met:

(a) actieve HOGE inputs en (b) actieve lage inputs.

De Karnaugh map-oplossing van JK flipflop met:

(c) actieve HOGE inputs en (d) actieve LAGE inputs.

De karakteristieke vergelijkingen voor de Karnaugh maps van de bovenstaande afbeelding zijn respectievelijk,

![]()

Basis symbool en circuit diagram van JK Flip Flop

Het symbool van deze JK-flipflop lijkt veel op dat van de S-R-flipflop zonder klokingang.

Het basissymbool van de JK-flipflop

Zoals hierboven vermeld, worden de vorige R- en S-ingangen nu vervangen door twee nieuwe ingangen: J en K. De ingangen worden J = S en K = R.

Als de R-S-flipflop twee 2-ingangen AND-poorten heeft, moeten we deze een beetje aanpassen om een JK-flipflop te maken.

We gebruiken twee 3-ingang NAND-poorten en de derde ingang van elke poort is verbonden met de uitgangen van Q en Q’. De NAND-poort voor de J-ingang krijgt de Q’-status, terwijl de NAND-poort voor de K-ingang de Q-status krijgt.

Deze kruisverbanden feedback kan de ongeldige conditie (S = R = 1 en S = R = 0) verwijderen, omdat de twee ingangen nu met elkaar zijn verbonden.

Sequentiële werking van JK Flip Flop

Hieronder ziet u het circuitdiagram van een JK-flipflop, bestaande uit 4 NAND’s. We richten ons alleen op de eerste twee NAND’s: NAND1 en NAND2.

Sequentiële werking van JK flipflop

Let nu op de JK flipflop sequentiële werking van JK flipflop hieronder:

- Veronderstel eerst dat zowel J als K logische ingangen 1, Q = 0, Q’ = 1 ontvangen.

- NAND1 is ingeschakeld.

- NAND1 heeft 2 logische toestanden “1” (J en Q’) van drie ingangen.

- NAND1 heeft alleen een logische toestand “1” nodig op zijn klok signaalingang om zijn uitgangstoestand logica te wijzigen naar “0”.

- Tot dit punt is de NAND2 nog steeds uitgeschakeld omdat hij slechts één logische toestand “1” heeft op zijn ingang K. Zijn feedback ingang is logische toestand “0” van Q.

- De klokpuls is HOOG.

- De uitgang van NAND1 verandert naar de logische toestand “0”.

- Dus, Q = 1 en Q’ = 0.

- NAND2 is ingeschakeld en NAND1 is uitgeschakeld.

Er is een probleem wanneer de logische status aan de uitvoerzijde verandert. Als het kloksignaal nog steeds HOOG is of in de overgangsperiode ‘HOOG naar LAAG’ wanneer de flipflop zijn logische status verandert, zal de uitvoer van NAND2 bijna onmiddellijk veranderen naar logische status “0”.

Dit timing probleem zal de flipflop resetten naar zijn allereerste status. Omdat dit probleem optrad, zal de flipflop zeer snel oscilleren tussen de logische statussen “0” en “1”.

U zult dit probleem een Race-Around Flip-Flop-probleem noemen. De naam impliceert de ‘race’ van de uitvoergegevens rond de feedback route van uitvoer naar invoer vóór het einde van het kloksignaal.

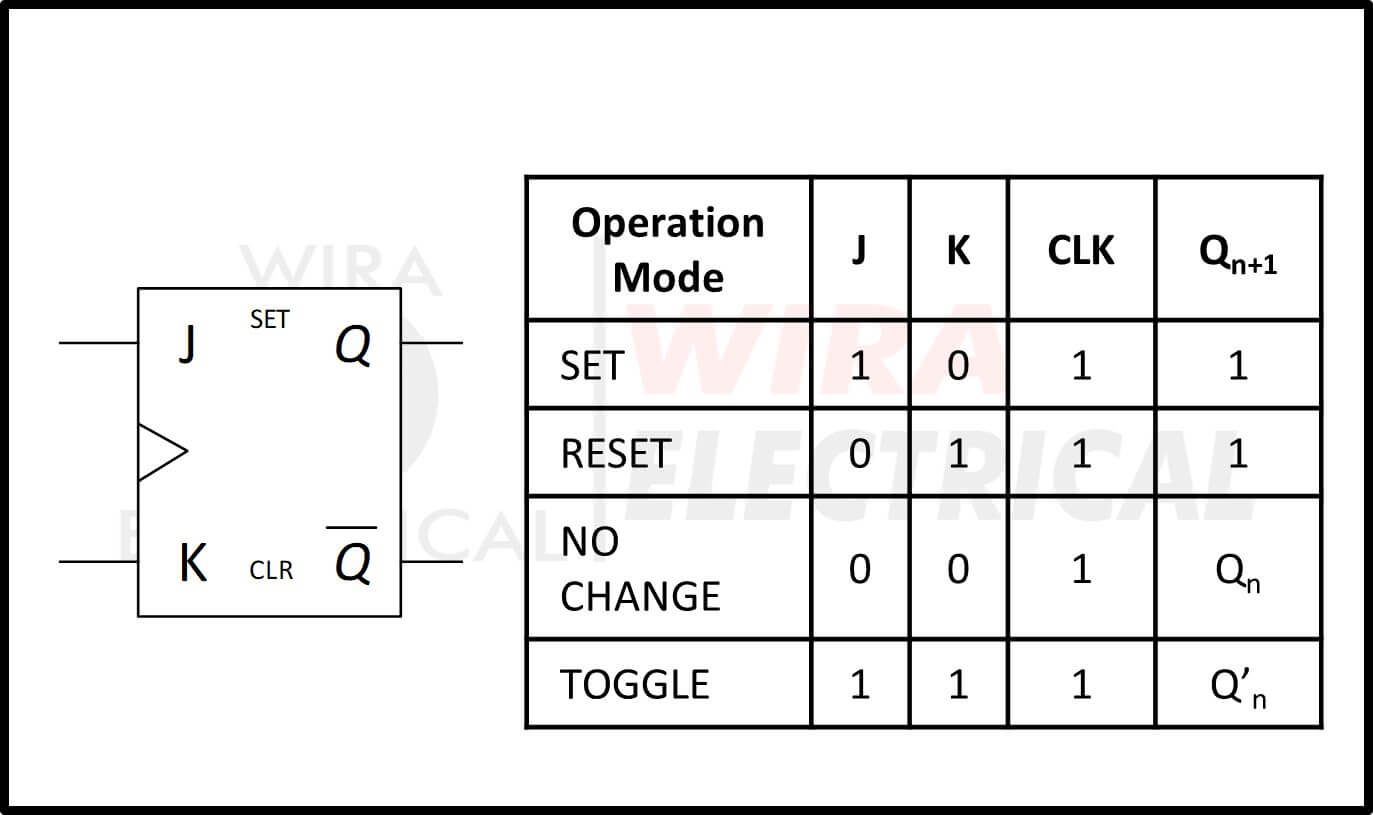

Waarheidstabel van JK Flip Flop

Omdat Q en Q’ altijd verschillend zijn, kunnen we ze gebruiken om de invoer te regelen. Wanneer beide invoer J en K gelijk zijn aan logische “1”, schakelt de JK flipflop om zoals weergegeven in de volgende waarheidstabel.

Omdat Q en Q’ altijd verschillend zijn, kunnen we de uitvoer gebruiken om de invoer te regelen. Als de J en K beide actief HIGH of logische status “1” zijn, schakelt de JK flipflop de uitvoer om zoals weergegeven in de onderstaande tabel.

Waarheidstabel van JK Flip Flop

Zoals hierboven vermeld, heeft de JK flipflop hetzelfde basisprincipe als de R-S flipflop. De JK flipflop heeft kruis feedback naar een van de twee ingangen. Deze feedbacks activeren de SET of RESET op een bepaald moment, waardoor de verboden ingang combinatie wordt geëlimineerd.

Niet alleen dat, als we zowel de J- als de K-ingangen tegelijkertijd de logische status “1” geven, zal dit ook niet resulteren in een ongeldige status. Wanneer de klokpuls HOOG is terwijl J = K = 1, zal het circuit zijn status veranderen van SET naar RESET of vice versa.

We kunnen aannemen dat deze flipflop functioneert als een T flip flop wanneer beide ingangen HOOG zijn.

Zelfs deze JK flipflop is de verbeterde R-S flipflop, deze heeft één nadeel. Het timingsprobleem genaamd “race” treedt op wanneer de uitgang Q de logische status verandert voordat de timing puls van de klok signaalingang niet “UIT” is gegaan.

Om dit probleem op te lossen, moeten we de puls periode (T) bij hoge frequenties zo kort mogelijk houden.

JK Flip Flop met Preset en Clear

Vaak moeten we de flipflop CLEAR naar logische toestand “0” (Qn = 0) of PRESET naar logische toestand “1” (Qn = 1). Er is een voorbeeld in de onderstaande afbeelding. Het laat zien hoe we het doen.

JK flipflop met PRESET en CLEAR

Er zijn twee voorwaarden:

- De flip flop wordt gewist (Qn = 0) als we de CLEAR-ingangen een logische status “0” geven en de PRESET-ingang een logische status “1”.

- De flip flop bevindt zich in de vooraf ingestelde logische status “1” (Qn = 1) als we de CLEAR-ingangen een logische status “1” geven en de PRESET-ingangen een logische status “0”.

Hier zijn de PRESET- en CLEAR-ingangen actief wanneer ze laag zijn.

JK flip flop met PRESET en CLEAR

De afbeelding hierboven is het circuit symbool van een geklokte JK flipflop die vooraf instelbaar en wisbaar is.

De waarheidstabel van JK flipflop met PRESET en CLEAR

De tabel hierboven is de waarheidstabel van JK flipflop met PRESET en CLEAR.

Uit de tabel concluderen we dat, als de PRESET-ingang actief is, de uitgang verandert naar logische status “1”, ongeacht de status van de klok, J en K-ingangen.

Anders, als de CLEAR-ingang actief is, verandert de uitgang naar logische status “0”, ongeacht de status van de klok, J en K-ingangen.

Er is een uitzondering voor deze JK flipflop met PRESET en CLEAR: beide PRESET- en CLEAR-ingangen mogen niet tegelijkertijd worden geactiveerd.

Master Slave JK Flip Flop-circuit diagram en waarheidstabel

Wanneer de breedte van de klokpuls van de flipflop groter is dan de vertraging van de voortplanting van de flipflop, is de verandering van de uitvoer van de flipflop niet betrouwbaar.

Om dit probleem te verhelpen, gebruiken we de puls die wordt gegenereerd door de edge-triggered flipflop. Deze puls die wordt gegenereerd door het edge-detector gedeelte van de flipflop zou de trigger zijn, in plaats van de pulsbreedte die wordt gegenereerd door het klok invoersignaal.

Dit fenomeen wordt een race probleem genoemd. Omdat de voortplanting vertraging meestal erg klein is, is de kans op race condities vrij groot.

De meest bekende oplossing om dit probleem op te lossen, is het gebruik van de slave-master flipflopconfiguratie.

Master-slave JK flipflop

Hierboven ziet u de master-slave JK flipflop die is opgebouwd uit twee JK flipflops. Dit type flip flop bestaat uit twee delen:

- De eerste flipflop = de master flipflop

- De tweede flipflop = de slave flipflop

De klok signaalinvoer wordt aangevuld met de slave flipflop, terwijl de master het klok invoersignaal rechtstreeks ontvangt.

De bewerkingsstappen van deze master-slave JK flipflop zijn:

- De kloksignaal puls is HOOG,

- De master flipflop is ingeschakeld, maar de slave flipflop is uitgeschakeld,

- Als gevolg hiervan kan de master flipflop zijn uitvoerlogicastatus wijzigen, maar de slave flipflop niet,

- De kloksignaal puls is LAAG,

- De master flipflop is uitgeschakeld, maar de slave flipflop is ingeschakeld,

- Daarom verandert de logische status van de slave JK flipflop volgens de logische status JK logische ingangen.

- De logische status van de master flipflop wordt overgebracht naar de slave flipflop en de uitgeschakelde master flipflop kan nieuwe ingangen verkrijgen zonder de uitgang te beïnvloeden.

Uit de bovenstaande stappen zou het duidelijk moeten zijn dat een master-slave flipflop een puls-getriggerde flipflop is, geen edge-getriggerde flipflop.

De onderstaande tabel toont ons de waarheidstabel van een master-slave JK flipflop samen met actieve LOW PRESET en CLEAR ingangen, en ook de actieve HIGH J en K ingangen.

Maar de master-slave JK flipflop is verouderd. De moderne IC’s zoals 74LS, 74AL, 74ALS, 74HC en 74HCT hebben geen master-slave flip flops in hun serie.

Hieronder zullen we zien hoe de master-slave van de JK flipflop werkt met behulp van het circuit diagram.

Bekijk een paar JK flipflops hieronder die een Master Slave JK Flip Flop Circuit Diagram vormen.

Master Slave JK flipflop

Beide ingangssignalen J, K en klokingang zijn verbonden met de “master” R-S flipflop die de ingangen kan vergrendelen wanneer het klok ingangssignaal ‘CLK’ HOOG is of in logische toestand “1” staat.

Het CLK-signaal wordt aangevuld als de timing puls voor de “slave” R-S flipflop. Hierdoor werken beide flipflops afwisselend.

Als we kijken naar het bovenstaande schema, kunnen we de stappen als volgt concluderen:

- CLK is HOOG of in logische toestand “1”

- CLK-ingang is in logische toestand “1” voor de “master” en “0” voor de “slave”

- De ingangen van de “master” zijn vergrendeld, maar de uitgangen worden alleen gezien door de “slave”-flipflop.

- CLK is LAAG of in logische toestand “0”

- CLK-ingang is in logische toestand “0” voor de “master” en “1” voor de “slave”

- De uitgangen van de “master” zijn vergrendeld en de flipflop leest geen ingangen.

- De “slave”-flipflop leest zijn ingang van de overgedragen uitgangen van de “master”

Het is vrij interessant dat de overgang van “LOW naar HIGH” van het kloksignaal een grote rol zal spelen in deze JK flipflop.

‘LOW naar HIGH’: de “master” zal zijn outputs overdragen. Deze overgang wordt aangevuld met de “slave” als ‘HIGH naar LOW’ en zorgt ervoor dat de inputs worden verwerkt door de “slave”.

Deze timingbewerking zorgt ervoor dat deze flipflop edge- of puls-getriggerd is.

De flipflop ontvangt de inputlogicastatus wanneer de CLK HIGH is en stuurt de data naar de output wanneer het kloksignaal in een dalende edge is.

Daarom kunnen we aannemen dat de Master-Slave JK flipflop een “synchroon” elektrisch apparaat is, omdat het alleen data verzendt bij specifieke klokinvoertiming.

Voor een master slave JK flipflop met preset en clear kunnen we het eenvoudig maken vanuit het diagram van de JK flipflop met preset en clear hierboven plus een JK flipflop.

De tabel met karakteristieken van de master-slave-jk-flipflop is hieronder te zien, waarbij elke puls sequentieel het paar JK-flipflops beïnvloedt.

De toestanden in de gele cellen worden overgebracht naar de blauwe cellen wanneer de CLK wordt geactiveerd.

Het nadeel van JK Flip Flop

Het belangrijkste en enige nadeel van de JK flipflop is hierboven genoemd, de Race Around Condition. Dit probleem treedt op wanneer de J en K inputs in logische status “1” staan.

De race around condition is wanneer de output de outputs meer dan één keer omschakelt nadat de output één keer is aangevuld.

Als dit probleem zich voordoet, zal het erg moeilijk zijn om de volgende outputs te voorspellen. Stel dat we J en K een logische status “1” geven, dan zal de output in de volgende klokpuls omschakelen.

Wat zal er gebeuren als de J en K hetzelfde blijven in logische status “1”?

De output zal nog één keer omschakelen en het patroon 0101010 in het echte scenario voortzetten. We hebben de master slave JK flipflop nodig om dit nadeel te voorkomen.

We moeten ook het klok interval kleiner maken dan de vertraagde voortplanting van de flipflop. Als dit niet wordt bereikt, kunnen de inputs de inputs niet lezen voordat de klokpuls verandert.

Populaire JK Flip Flop IC

Als u op zoek bent naar een JK flipflop IC, kunt u overwegen om de onderstaande OC te kopen:

- 74LS107: Dual JK Flip-Flop

- 74LS109: Dual JK Flip-Flop

- 74LS73: Dual JK Negative-Edge-Triggered Flip-Flop

- 74LS112: Dual JK Negative-Edge-Triggered Flip-Flop

- 74LS76: Dual JK Positive-Edge-Triggered Flip-Flop

- 74LS114: Dual JK Negative-Edge-Triggered Flip-Flops DIP-14

- 74LS78: Dual JK Negative-Edge-Triggered Flip-Flops DIP-14

- NTE74LS76A: TTL Dual JK Flip-Flop met Preset en Clear DIP-16

- 74LS113: Dual JK Negative-Edge-Triggered Flip-Flops DIP-14

Veelgestelde vragen

Nu gaan we proberen de veelgestelde vragen over JK flipflop te beantwoorden:

Wat is de JK flipflop waarheidstabel?

De JK flipflop is in principe de verbeterde versie van de R-S flipflop, maar de uitvoer blijft hetzelfde wanneer de J- en K-ingangen LAAG zijn. De sequentiële logische werking van deze JK flipflop is hetzelfde als de R-S flipflop met dezelfde SET- en RESET-logische ingangen. Het enige verschil is dat de JK flipflop geen verboden invoer combinatie heeft.

Wat is de werking van de JK flipflop?

De JK flipflop heeft verschillende ingangen: J, K, S en R die kunnen worden gebruikt zoals elk ander type flipflop. De JK flipflop is in principe de verbeterde versie van de R-S flipflop, maar de uitvoer blijft hetzelfde wanneer de J- en K-ingangen LAAG zijn. Deze flipflop is een combinatie van een gated R-S flipflop en een geklokte signaalang.

Wat is een JK flipflop met een logisch diagram?

Omdat Q en Q’ altijd verschillend zijn, kunnen we ze gebruiken om de invoer te regelen. Wanneer beide invoer J en K gelijk zijn aan logische “1”, schakelt de JK flipflop. Omdat Q en Q’ altijd verschillend zijn, kunnen we de uitvoer gebruiken om de invoer te regelen. Als de J en K beide actief HOOG of logische status “1” zijn, schakelt de JK flipflop de uitvoer om

Wat is het nadeel van de JK flipflop?

Het belangrijkste en enige nadeel van de JK flipflop is hierboven genoemd, de Race Around Condition. Dit probleem treedt op wanneer de invoer J en K zich in logische status “1” bevinden. De race around condition is wanneer de uitvoer de uitvoer meer dan één keer omschakelt nadat de uitvoer één keer is aangevuld.

Waarom wordt de JK flipflop een universele flip flop genoemd?

De JK flipflop wordt beschouwd als een universele programmeerbare flipflop. De JK flipflop heeft verschillende invoer: J, K, S en R die kunnen worden gebruikt zoals elk ander type flipflop. De JK-flipflop is in principe de verbeterde versie van de R-S-flipflop, maar de uitvoer blijft hetzelfde wanneer de J- en K-ingangen LAAG zijn.