JK Flip Flop is considered to be a universal programmable flip flop. Why is it considered to be a universal flip flop?

JK flip flop has several inputs: J, K, S, and R which can be used like any other flip flop types. The JK flip flop is basically the improved version of the R-S flip flop but the output remains the same when the J and K inputs are LOW.

The R-S flip flop circuit may have many advantages and functions in logic circuits but it has two major problems:

- Set = Reset = 0 (S = R = 0) and Set = Reset = 1 (S = R = 1) must be avoided

- If the SET or RESET inputs change logic state when the Clock (CLK) is active HIGH, the correct latching action may not happen.

To solve these major problems, the JK flip flop was constructed.

We can say that the JK flip flop is the most versatile flip flop, because it has inputs like D flip flop with clock input. This flip flop uses two inputs labeled with J and K.

If the J and K input are different, the output Q will have the value of J at the next clock edge cycle. J and K is used to give honor to Jack Kilby as the inventor of this flip flop type.

We need to understand how JK flip flop works first before learning about a Master Slave JK flip flop truth table.

What is JK Flip Flop

This basic JK flip flop is the most mainly used of all the flip flop circuits and is known as a universal flip flop. This flip flop’s inputs are labeled with “J” and “K” just like “S” for SET and “R” for RESET in S-R flip flop.

The J and K stand for Jack Kilby as this flip flop type inventor.

The sequential logic operation of this JK flip flop is the same with the R-S flip flop with the same SET and RESET logic inputs. The only difference is the JK flip flop has no forbidden input combination.

JK flip flop or JK-FF for short, is basically an improved R-S flip flop. This flip flop is a combination of a gated R-S flip flop and a clocked signal input.

The clock input will prevent the invalid or illegal input operation when both S and R equal to logic “1”.

Using this clocked input, the JK flip flop will produce four different input combination:

- Logic “1”

- Logic “0”

- No change

- Toggle.

There are two responses of JK flip flop:

- When the J and J inputs are both in low state (logic “0”) = no change happens

- When the J and K inputs are both in high state (logic “1”) at the clock edge = the output will change from one logic state to the other (“0” to “1” and vice versa)

This JK flip flop can exactly act as an R-S flip flop while eliminating the ambiguous conditions.

Not only that, but this flip flop can also imitate a T flip flop to do the output flip flop if we tie the J and K inputs together.

This toggle application can be used for extensive binary counters.

The JK flip flop has the same function as the R-S flip flop, but for one of the responses in the truth table.

The disadvantage of R-S flip flop is the prohibited input combinations below:

- The inputs S = R = 1 (active HIGH logic inputs)

- The inputs S = R = 0 (active LOW logic inputs)

This disadvantage of R-S flip flop has been overcome by JK flip flop in case:

- Active HIGH inputs, the output of the flip flop switch, hence, it changes to the other logic state (for J = K = 1)

- Active LOW inputs, the output of the flip flop switch, hence, it changes to the other logic state (for J = K = 1)

JK flip flop active high inputs

JK flip flop active low inputs

Figures above represent the circuit symbol of level-triggered JK flip flop with active HIGH and LOW inputs respectively, along with the truth table.

Representation of the JK flip flop using an R-S flip flop

The figure above shows us the JK flip flop from R-S flip flop with additional logic gates.

The truth tables of JK flip flop and the Karnaugh map solutions

The tables above show us the truth tables of JK flip flop with:

(a) active HIGH inputs and (b) active low inputs.

The Karnaugh map solution of JK flip flop with:

(c) active HIGH inputs and (d) active LOW inputs.

The characteristic equations for the Karnaugh maps of the figure above are respectively,

![]()

Basic Symbol and Circuit Diagram of JK Flip Flop

The symbol of this JK flip flop is quite similar to the S-R flip flop without the clock input.

The basic symbol of JK flip flop

Like mentioned above, the previous R and S inputs are now replaced by two new inputs: J and K. The inputs become J = S and K = R.

If the R-S flip flop has two 2-inputs AND gates, we need to modify it a little to make a JK flip flop.

We will use two 3-input NAND gates and the third input of each gate connected with the outputs of Q and Q’. The NAND gate for J input gets the Q’ state while the NAND gate for K input gets the Q state.

This cross-connected feedback is able to get rid of the invalid condition (S = R = 1 and S = R = 0) because the two inputs are now interlocked.

Sequential Operation of JK Flip Flop

Below is the circuit diagram of a JK flip flop, consisting of 4 NANDs. We will only focus on the first two NANDs: NAND1 and NAND2.

Sequential operation of JK flip flop

Now pay attention to the JK flip flop sequential operation of JK flip flop below:

- First, assume that both J and K receive logic inputs 1, Q = 0, Q’ = 1.

- NAND1 is enabled.

- NAND1 has 2 logic states “1” (J and Q’) from three inputs.

- NAND1 only needs a logic state “1” on its clock signal input to change its output state logic to “0”.

- Until this point, the NAND2 is still disabled because it only has one logic state “1” on its input K. Its feedback input is logic state “0” from Q.

- The clock pulse is HIGH.

- The output of NAND1 changes to the logic state “0”.

- So, Q = 1 and Q’ = 0.

- NAND2 is enabled and NAND1 is disabled.

There is a problem when the logic state changes at the output side. If the clock signal is still HIGH or in the transition period ‘HIGH to LOW’ when the flip flop changes its logic state, the output of NAND2 will change to logic state “0” almost instantly.

This timing problem will reset the flip flop to its very first state. Because this problem occurred, the flip flop will oscillate between the logic states “0” and “1” very quickly.

You will call this problem a Race-Around Flip-Flop problem. The name implies the ‘race’ of the output data around the feedback route from output to input before the end of the clock signal.

Truth Table of JK Flip Flop

As Q and Q’ are always different we can use them to control the input. When both inputs J and K are equal to logic “1”, the JK flip flop toggles as shown in the following truth table.

Because Q and Q’ are always different, we can use the outputs to control the inputs. If the J and K are both active HIGH or logic state “1”, the JK flip flop will toggle the outputs as shown in the table below.

Truth Table of JK Flip Flop

Like mentioned above, the JK flip flop has the same basic principle as R-S flip flop. The JK flip flop has cross feedback to one of the two inputs. These feedbacks will activate the SET or RESET at one time, hence eliminating the forbidden input combination.

Not only that, if we give both the J and K inputs logic state “1” at the same time, but it also will not result in an invalid state. When the clock pulse is HIGH while J = K = 1 then the circuit will change its state from SET to RESET or vice versa.

We can assume this flip flop is functioning as a T flip flop when both inputs are HIGH.

Even this JK flip flop is the improved R-S flip flop, this one has one disadvantage. The timing problem called “race” occurs when the output Q changes the logic state before the timing pulse of the clock signal input has not gone “OFF”.

In order to eliminate this problem, we must keep the pulse period (T) as short as possible with high frequency.

JK Flip Flop with Preset and Clear

Often we need to CLEAR the flip flop to logic state “0” (Qn = 0) or PRESET it to logic state “1” (Qn = 1). There is an example in the figure below. It will show how we do it.

JK flip flop with PRESET and CLEAR

There are two conditions:

- The flip flop will be cleared (Qn = 0) if we give logic state “0” to the CLEAR inputs and logic state “1” to the PRESET input.

- The flip flop is in preset logic state “1” condition (Qn = 1) if we give logic state “1” to the CLEAR inputs and logic state “0” to the PRESET inputs.

Here, the PRESET and CLEAR inputs are active when low.

JK flip flop with PRESET and CLEAR

The image above is the circuit symbol of a clocked JK flip flop which is presettable and clearable.

The truth table of JK flip flop with PRESET and CLEAR

The table above is the truth table of JK flip flop with PRESET and CLEAR.

From the table, we conclude that, if the PRESET input is active, the output changes to logic state “1” regardless of the status of the clock, J, and K inputs.

Otherwise, if the CLEAR input is active, the output changes to logic state “0” regardless of the status of the clock, J, and K inputs.

There is an exception for this JK flip flop with PRESET and CLEAR: both of the PRESET and CLEAR inputs should not be activated at the same time.

Master Slave JK Flip Flop Circuit Diagram and Truth Table

When the width of the clock pulse of the flip flop is greater than the delay of the flip flop’s propagation, the change of the flip flop’s output is not reliable.

To overcome this problem, we will use the pulse generated by the edge-triggered flip flop. This pulse generated by the edge-detector portion of the flip flop would be the trigger, instead of the pulse width generated by the clock input signal.

This phenomenon is referred to as a race problem. Because the propagation delay is usually very small, the likelihood of race conditions occurring is quite high.

The most known solution to solve this problem is to use the slave-master flip flop configuration.

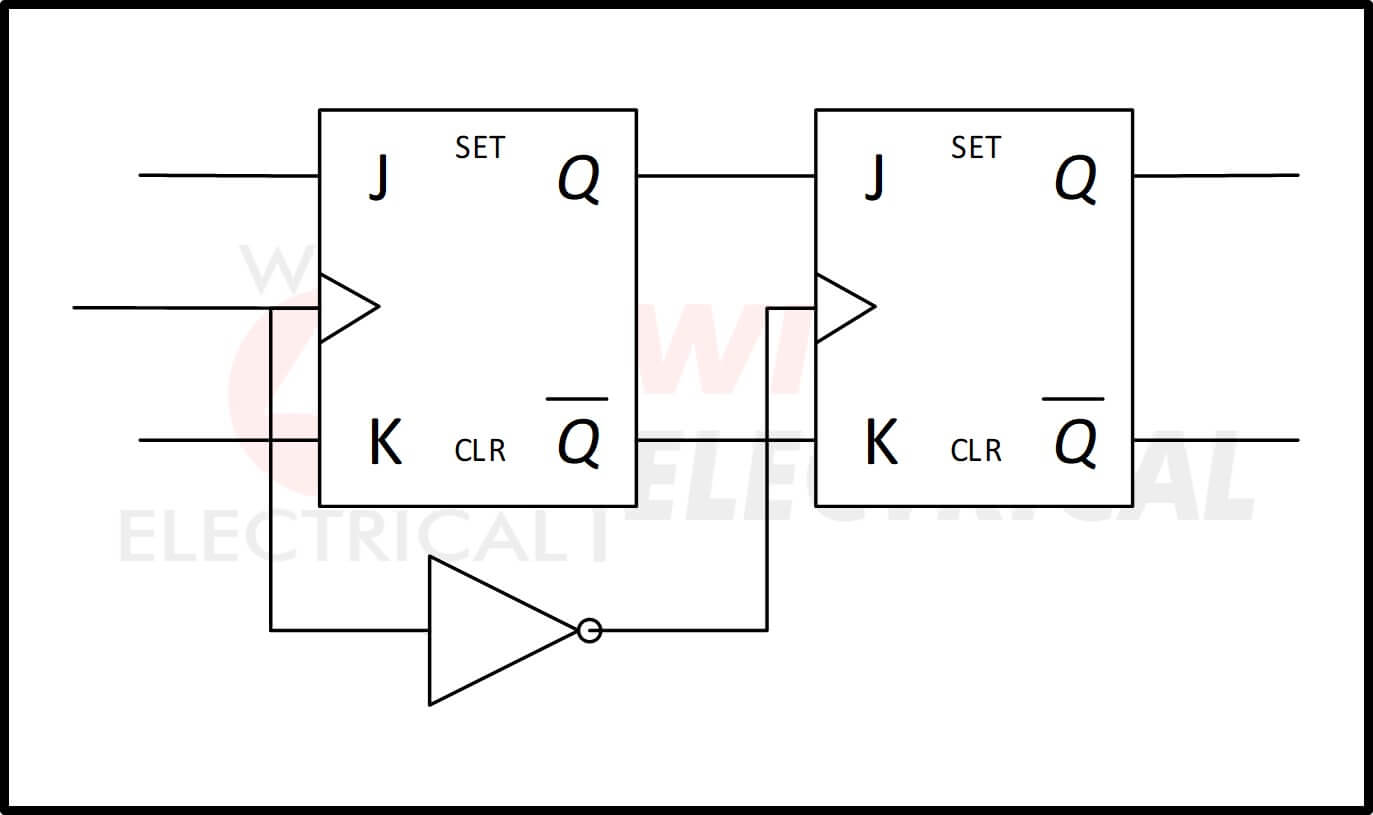

Master-slave JK flip flop

Above is the master-slave JK flip flop built with two JK flip flops. There are two parts of this type of flip flop:

- The first flip flop = the master flip flop

- The second flip flop = the slave flip flop

The clock signal input will be complemented to the slave flip flop, while the master receives the clock input signal directly.

The operation steps of this master-slave JK flip flop are:

- The clock signal pulse is HIGH,

- The master flip flop is enabled, but the slave flip flop is disabled,

- As the result, the master flip flop is able to change its output logic state, but the slave flip flop is unable,

- The clock signal pulse is LOW,

- The master flip flop is disabled, but the slave flip flop is enabled,

- Hence, the logic state of the slave JK flip flop changes as per logic state JK logic inputs.

- The logic state of the master flip flop is transferred to the slave flip flop, and the disabled master flip flop can acquire new inputs without affecting the output.

From the steps above, it should be clear that a master-slave flip flop is a pulse-triggered flip flop, not an edge-triggered flip flop.

The table below will show us the truth table of a master-slave JK flip flop along with active LOW PRESET and CLEAR inputs, and also the active HIGH J and K inputs.

But, the master-slave JK flip flop has become obsolete. The modern IC such as 74LS, 74AL, 74ALS, 74HC, and 74HCT don’t have master-slave flip flops in their series.

Below we will observe how the master slave of the JK flip flop works using its circuit diagram.

Observe a pair of JK flip flop below form a Master Slave JK Flip Flop Circuit Diagram.

Master Slave JK flip flop

Both input signals J, K, and clock input are connected to the “master” R-S flip flop which is able to lock the inputs when the clock input ‘CLK’ signal is HIGH or at logic state “1”.

The CLK signal is complemented as the timing pulse for the “slave” R-S flip flop. This will make both flip flops work alternately.

Looking from the circuit diagram above, we can conclude the steps as:

- CLK is HIGH or at logic state “1”

- CLK input is at logic state “1” for the “master” and “0” for the “slave”

- The inputs of the “master” are locked, but the outputs are only seen by the “slave” flip flop.

- CLK is LOW or at logic state “0”

- CLK input is at logic state “0” for the “master” and “1” for the “slave”

- The outputs from the “master” are latched and the flip flop does not read any inputs.

- The “slave” flip flop is reading its input from the transferred outputs from the “master”

It is quite interesting that the “LOW to HIGH” transition of the clock input signal will play a huge role in this JK flip flop.

’LOW to HIGH’: the “master” will transfer its outputs. This transition is complemented to the “slave” as ‘HIGH to LOW’ and makes the inputs processed by the “slave”.

This timing operation makes this flip flop as edge or pulse-triggered.

The flip flop receives input logic state when the CLK is HIGH and sends the data to the output when the clock signal is in falling-edge.

Hence, we can assume that the Master-Slave JK flip flop is a “Synchronous” electric device because it only sends data at specific clock input timing.

For a master slave JK Flip Flop with preset and clear we can easily make it from the diagram of the JK Flip Flop with preset and clear above plus a JK flip flop.

The master slave jk flip flop characteristic table can be observed below where each pulse affects the pair of JK flip flop sequentially.

The states in yellow color cells will be transferred to blue color cells when the CLK is triggered.

The Drawback of JK Flip Flop

The main and the only drawback of the JK flip flop has been mentioned above, the Race Around Condition. This problem occurs when the J and K inputs are in logic state “1”.

The race around condition is when the output toggles the outputs more than one time after the output is complemented once.

If this problem happens, it will be very difficult to predict the next outputs. Assume if we give J and K a logic state “1”, in the next clock pulse the output will toggle.

What will happen if the J and K remain same at logic state “1”?

The output will toggle one more time and continue the pattern 0101010 in the real scenario.. We need the master slave JK flip flop in order to prevent this drawback.

We also need the clock interval to be less than the delay propagation of the flip flop. If this is not achieved, the inputs won’t be able to read the inputs before the clock pulse changes.

Popular JK Flip Flop IC

If you are looking for JK flip flop IC, you may consider buying the IC listed below:

- 74LS107 : Dual JK Flip-Flop

- 74LS109 : Dual JK Flip-Flop

- 74LS73 : Dual JK Negative-Edge-Triggered Flip-flop

- 74LS112 : Dual JK Negative-Edge-Triggered Flip-flop

- 74LS76 : Dual JK Positive-Edge-Triggered Flip-Flop

- 74LS114 : Dual JK Negative-Edge-Triggered Flip-Flops DIP-14

- 74LS78 : Dual JK Negative-Edge-Triggered Flip-Flops DIP-14

- NTE74LS76A : TTL Dual JK Flip-Flop with Preset and Clear DIP-16

- 74LS113 : Dual JK Negative-Edge-Triggered Flip-Flops DIP-14

Frequently Asked Questions

Now we will try to answer the frequently asked questions about JK flip flop:

What is the JK flip flop truth table?

The JK flip flop is basically the improved version of the R-S flip flop but the output remains the same when the J and K inputs are LOW. The sequential logic operation of this JK flip flop is the same with the R-S flip flop with the same SET and RESET logic inputs. The only difference is the JK flip flop has no forbidden input combination.

What is the working of JK flip flop?

JK flip flop has several inputs: J, K, S, and R which can be used like any other flip flop types. The JK flip flop is basically the improved version of R-S flip flop but the output remains the same when the J and K inputs are LOW. This flip flop is a combination of a gated R-S flip flop and a clocked signal input.

What is a JK flip flop with a logic diagram?

As Q and Q’ are always different we can use them to control the input. When both inputs J and K are equal to logic “1”, the JK flip flop toggles. Because Q and Q’ are always different, we can use the outputs to control the inputs. If the J and K are both active HIGH or logic state “1”, the JK flip flop will toggle the outputs

What is the drawback of JK flip flop?

The main and the only drawback of the JK flip flop has been mentioned above, the Race Around Condition. This problem occurs when the J and K inputs are in logic state “1”. The race around condition is when the output toggles the outputs more than one time after the output is complemented once.

Why is the JK flip flop called a universal flip flop?

JK Flip Flop is considered to be a universal programmable flip flop. JK flip flop has several inputs: J, K, S, and R which can be used like any other flip flop types. The JK flip flop is basically the improved version of R-S flip flop but the output remains the same when the J and K inputs are LOW.

Hello my friend!

I want to say that this post is awesome, nice written and include approximately all significant infos.

I would like to see extra

posts like this .