Flip Flop JK dianggap sebagai flip flop universal yang dapat diprogram. Mengapa dianggap sebagai flip flop universal?

Flip flop JK memiliki beberapa input: J, K, S, dan R yang dapat digunakan seperti jenis flip flop lainnya. Flip flop JK pada dasarnya adalah versi perbaikan dari flip flop R-S tetapi outputnya tetap sama ketika input J dan K RENDAH.

Rangkaian flip flop R-S mungkin memiliki banyak keuntungan dan fungsi dalam rangkaian logika tetapi memiliki dua masalah utama:

- Set = Reset = 0 (S = R = 0) dan Set = Reset = 1 (S = R = 1) harus dihindari. Jika input SET atau RESET mengubah status logika saat Clock (CLK) aktif HIGH, tindakan penguncian yang benar mungkin tidak terjadi.

Untuk mengatasi masalah-masalah utama tersebut, maka dibuatlah JK flip flop.

Kita dapat mengatakan bahwa JK flip flop merupakan flip flop yang paling serbaguna, karena memiliki input seperti flip flop D dengan input clock. Flip flop ini menggunakan dua input yang diberi label J dan K.

Jika input J dan K berbeda, output Q akan memiliki nilai J pada siklus tepi clock berikutnya. J dan K digunakan untuk memberi penghormatan kepada Jack Kilby sebagai penemu flip flop jenis ini.

Kita perlu memahami cara kerja JK flip flop terlebih dahulu sebelum mempelajari tabel kebenaran Master Slave JK flip flop.

Apa itu JK Flip Flop

Flip-flop JK dasar ini adalah yang paling banyak digunakan dari semua rangkaian flip-flop dan dikenal sebagai flip-flop universal. Input flip-flop ini diberi label “J” dan “K” seperti “S” untuk SET dan “R” untuk RESET pada flip-flop S-R.

J dan K adalah singkatan dari Jack Kilby sebagai penemu tipe flip-flop ini.

Operasi logika sekuensial flip-flop JK ini sama dengan flip-flop R-S dengan input logika SET dan RESET yang sama. Satu-satunya perbedaan adalah flip-flop JK tidak memiliki kombinasi input yang dilarang.

Flip-flop JK atau disingkat JK-FF, pada dasarnya adalah flip-flop R-S yang telah disempurnakan. Flip-flop ini merupakan kombinasi dari flip-flop R-S yang berpagar dan input sinyal yang di-clock.

Input clock akan mencegah operasi input yang tidak valid atau ilegal ketika S dan R sama dengan logika “1”.

Dengan menggunakan input yang di-clock ini, flip-flop JK akan menghasilkan empat kombinasi input yang berbeda:

- Logika “1”

- Logika “0”

- Tidak ada perubahan

- Toggle.

Ada dua tanggapan dari JK yang berubah-ubah:

- Ketika input J dan J keduanya dalam status rendah (logika “0”) = tidak terjadi perubahan

- Ketika input J dan K keduanya dalam status HIGH (logika “1”) di tepi clock = output akan berubah dari satu status logika ke status logika lainnya (“0” ke “1” dan sebaliknya)

Flip-flop JK ini dapat bertindak persis seperti flip-flop R-S sekaligus menghilangkan kondisi ambigu.

Tidak hanya itu, flip-flop ini juga dapat meniru flip-flop T untuk melakukan flip-flop output jika kita menggabungkan input J dan K.

Aplikasi toggle ini dapat digunakan untuk penghitung biner yang ekstensif.

Flip-flop JK memiliki fungsi yang sama dengan flip-flop R-S, tetapi untuk salah satu respons dalam tabel kebenaran.

Kekurangan flip-flop R-S adalah kombinasi input yang dilarang di bawah ini:

- Input S = R = 1 (input logika HIGH aktif)

- Input S = R = 0 (input logika LOW aktif)

Kerugian dari R-S flip flop ini telah diatasi oleh JK flip flop dalam hal:

- Input HIGH yang aktif, output dari saklar flip flop, oleh karena itu, berubah ke status logika yang lain (untuk J = K = 1)

- Input LOW yang aktif, output dari saklar flip flop, oleh karena itu, berubah ke status logika yang lain (untuk J = K = 1)

Flip-flop JK aktif masukan HIGH

Flip-flop JK aktif masukan rendah

Gambar di atas merupakan simbol rangkaian flip-flop JK yang dipicu level dengan input HIGH dan LOW yang aktif, beserta tabel kebenarannya.

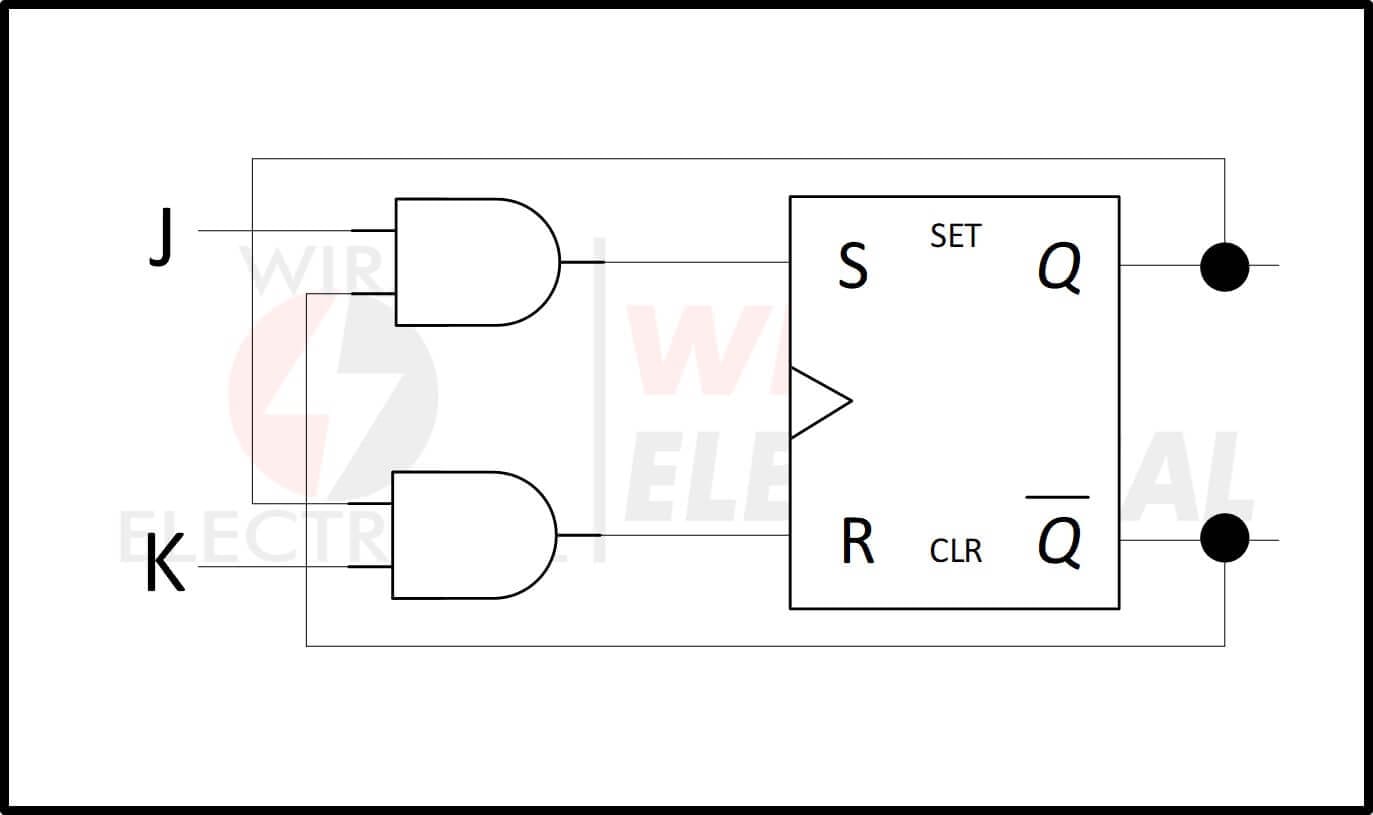

Representasi JK flip flop menggunakan R-S flip flop

Gambar di atas menunjukkan JK flip flop dari R-S flip flop dengan gerbang logika tambahan.

Tabel kebenaran flip-flop JK dan solusi pemetaan Karnaugh

Tabel di atas menunjukkan tabel kebenaran flip-flop JK dengan:

(a) input HIGH aktif dan (b) input low aktif.

Solusi pemetaan Karnaugh flip-flop JK dengan:

(c) input HIGH aktif dan (d) input LOW aktif.

Persamaan karakteristik untuk pemetaan Karnaugh pada gambar di atas masing-masing adalah,

![]()

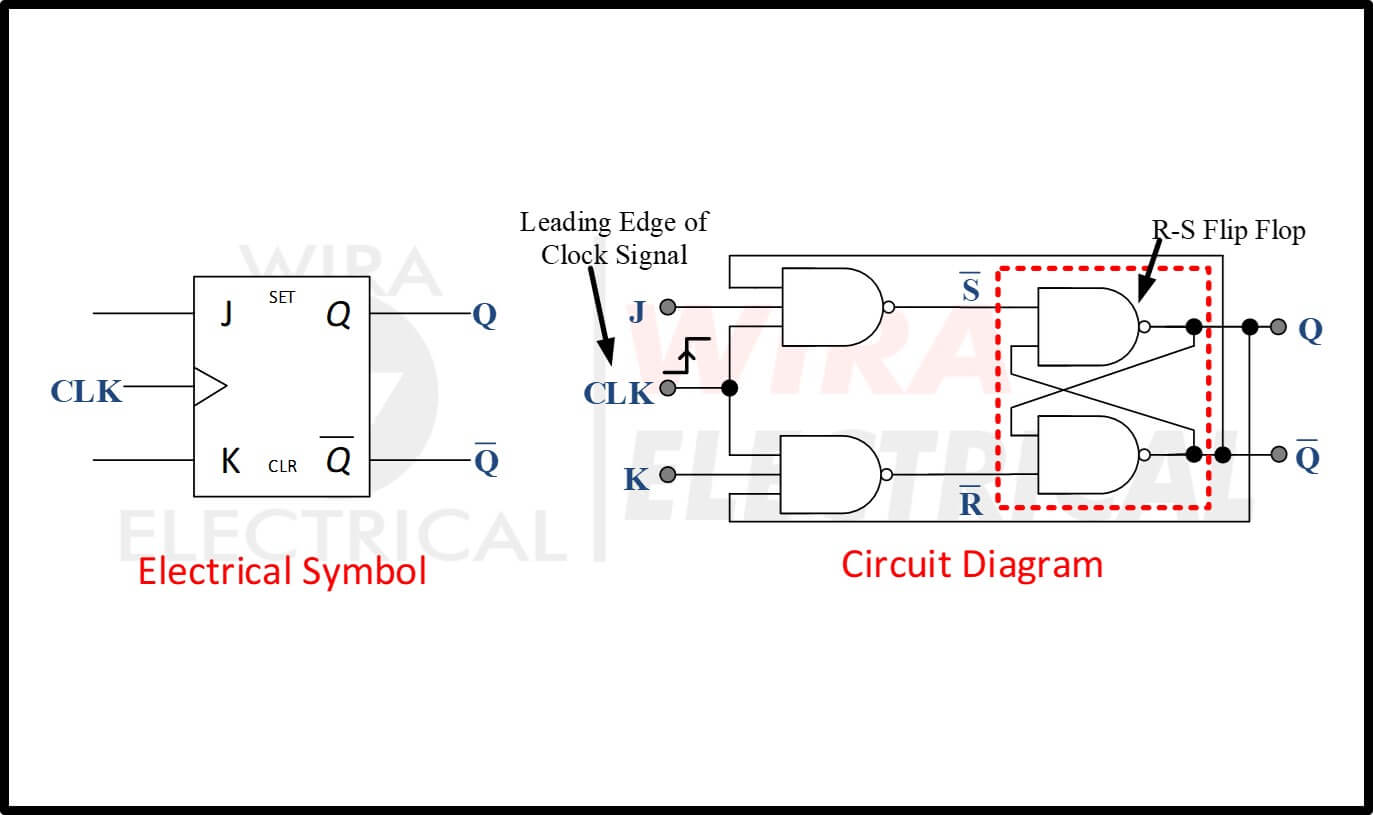

Simbol Dasar dan Diagram Rangkaian JK Flip Flop

Simbol flip flop JK ini cukup mirip dengan flip flop S-R tanpa masukan jam.

Simbol dasar JK flip flop

Seperti yang disebutkan di atas, input R dan S sebelumnya kini digantikan oleh dua input baru: J dan K. Input menjadi J = S dan K = R.

Jika flip flop R-S memiliki dua gerbang AND 2-input, kita perlu sedikit memodifikasinya untuk membuat flip flop JK.

Kita akan menggunakan dua gerbang NAND 3-input dan input ketiga dari setiap gerbang dihubungkan dengan output Q dan Q’. Gerbang NAND untuk input J mendapatkan status Q’ sementara gerbang NAND untuk input K mendapatkan status Q.

Umpan balik yang terhubung silang ini mampu menyingkirkan kondisi yang tidak valid (S = R = 1 dan S = R = 0) karena kedua input sekarang saling terkait.

Operasi Sekuensial JK Flip Flop

Berikut ini adalah diagram rangkaian JK flip flop, yang terdiri dari 4 NAND. Kita hanya akan fokus pada dua NAND pertama: NAND1 dan NAND2.

Operasi sekuensial JK flip flop

Sekarang perhatikan operasi sekuensial JK flip flop di bawah ini:

- Pertama, asumsikan bahwa J dan K menerima masukan logika 1, Q = 0, Q’ = 1.

- NAND1 diaktifkan.

- NAND1 memiliki 2 status logika “1” (J dan Q’) dari tiga masukan.

- NAND1 hanya memerlukan status logika “1” pada masukan sinyal clock-nya untuk mengubah logika status keluarannya menjadi “0”.

- Sampai titik ini, NAND2 masih dinonaktifkan karena hanya memiliki satu status logika “1” pada masukan K-nya. Masukan umpan baliknya adalah status logika “0” dari Q.

- Pulsa clock adalah HIGH.

- Keluaran NAND1 berubah ke status logika “0”.

- Jadi, Q = 1 dan Q’ = 0.

- NAND2 diaktifkan dan NAND1 dinonaktifkan.

Ada masalah ketika status logika berubah di sisi output. Jika sinyal clock masih HIGH atau dalam periode transisi HIGH ke LOW ketika flip flop mengubah status logikanya, output NAND2 akan berubah ke status logika “0” hampir seketika.

Masalah pengaturan waktu ini akan mereset flip flop ke status awalnya. Karena masalah ini terjadi, flip flop akan berosilasi antara status logika “0” dan “1” dengan sangat cepat.

Anda akan menyebut masalah ini sebagai masalah Race-Around Flip-Flop. Namanya menyiratkan ‘perlombaan’ data output di sekitar rute umpan balik dari output ke input sebelum akhir sinyal clock.

Tabel Kebenaran JK Flip Flop

Karena Q dan Q’ selalu berbeda, kita dapat menggunakannya untuk mengendalikan input. Ketika kedua input J dan K sama dengan logika “1”, flip-flop JK akan beralih seperti yang ditunjukkan pada tabel kebenaran berikut.

Karena Q dan Q’ selalu berbeda, kita dapat menggunakan output untuk mengendalikan input. Jika J dan K keduanya aktif HIGH atau berstatus logika “1”, flip-flop JK akan beralih output seperti yang ditunjukkan pada tabel di bawah.

Tabel Kebenaran Flip-Flop JK

Seperti yang disebutkan di atas, flip-flop JK memiliki prinsip dasar yang sama dengan flip-flop R-S. Flip-flop JK memiliki umpan balik silang ke salah satu dari dua masukan. Umpan balik ini akan mengaktifkan SET atau RESET pada saat yang bersamaan, sehingga menghilangkan kombinasi masukan yang dilarang.

Tidak hanya itu, jika kita memberikan status logika “1” pada masukan J dan K secara bersamaan, tetapi juga tidak akan menghasilkan status yang tidak valid. Ketika pulsa clock berstatus HIGH sementara J = K = 1 maka rangkaian akan mengubah statusnya dari SET menjadi RESET atau sebaliknya.

Kita dapat mengasumsikan flip-flop ini berfungsi sebagai flip-flop T ketika kedua masukan berstatus HIGH.

Flip-flop JK ini meskipun merupakan flip-flop R-S yang telah disempurnakan, memiliki satu kelemahan. Masalah pengaturan waktu yang disebut “race” terjadi jika keluaran Q mengubah status logika sebelum pulsa pengaturan waktu dari masukan sinyal clock menjadi “OFF”.

Untuk menghilangkan masalah ini, kita harus menjaga periode pulsa (T) sesingkat mungkin dengan frekuensi tinggi.

Flip Flop JK dengan Preset dan Clear

Seringkali kita perlu MENGHAPUS flip flop ke status logika “0” (Qn = 0) atau MENETAPKANNYA ke status logika “1” (Qn = 1). Ada contoh pada gambar di bawah ini. Gambar tersebut akan menunjukkan cara melakukannya.

Flip-flop JK dengan PRESET dan CLEAR

Ada dua kondisi:

- Flip flop akan dikosongkan (Qn = 0) jika kita memberikan status logika “0” pada input CLEAR dan status logika “1” pada input PRESET.

- Flip flop berada dalam kondisi status logika preset “1” (Qn = 1) jika kita memberikan status logika “1” pada input CLEAR dan status logika “0” pada input PRESET.

Di sini, input PRESET dan CLEAR aktif saat LOW.

Flip-flop JK dengan PRESET dan CLEAR

Gambar di atas adalah simbol rangkaian flip-flop JK yang memiliki clock yang dapat dipreset dan diclear.

Tabel kebenaran flip-flop JK dengan PRESET dan CLEAR

Tabel di atas adalah tabel kebenaran flip-flop JK dengan PRESET dan CLEAR.

Dari tabel tersebut, kita simpulkan bahwa, jika input PRESET aktif, output berubah ke status logika “1” terlepas dari status clock, input J, dan K.

Jika tidak, jika input CLEAR aktif, output berubah ke status logika “0” terlepas dari status clock, input J, dan K.

Ada pengecualian untuk flip-flop JK ini dengan PRESET dan CLEAR: baik input PRESET maupun CLEAR tidak boleh diaktifkan pada saat yang bersamaan.

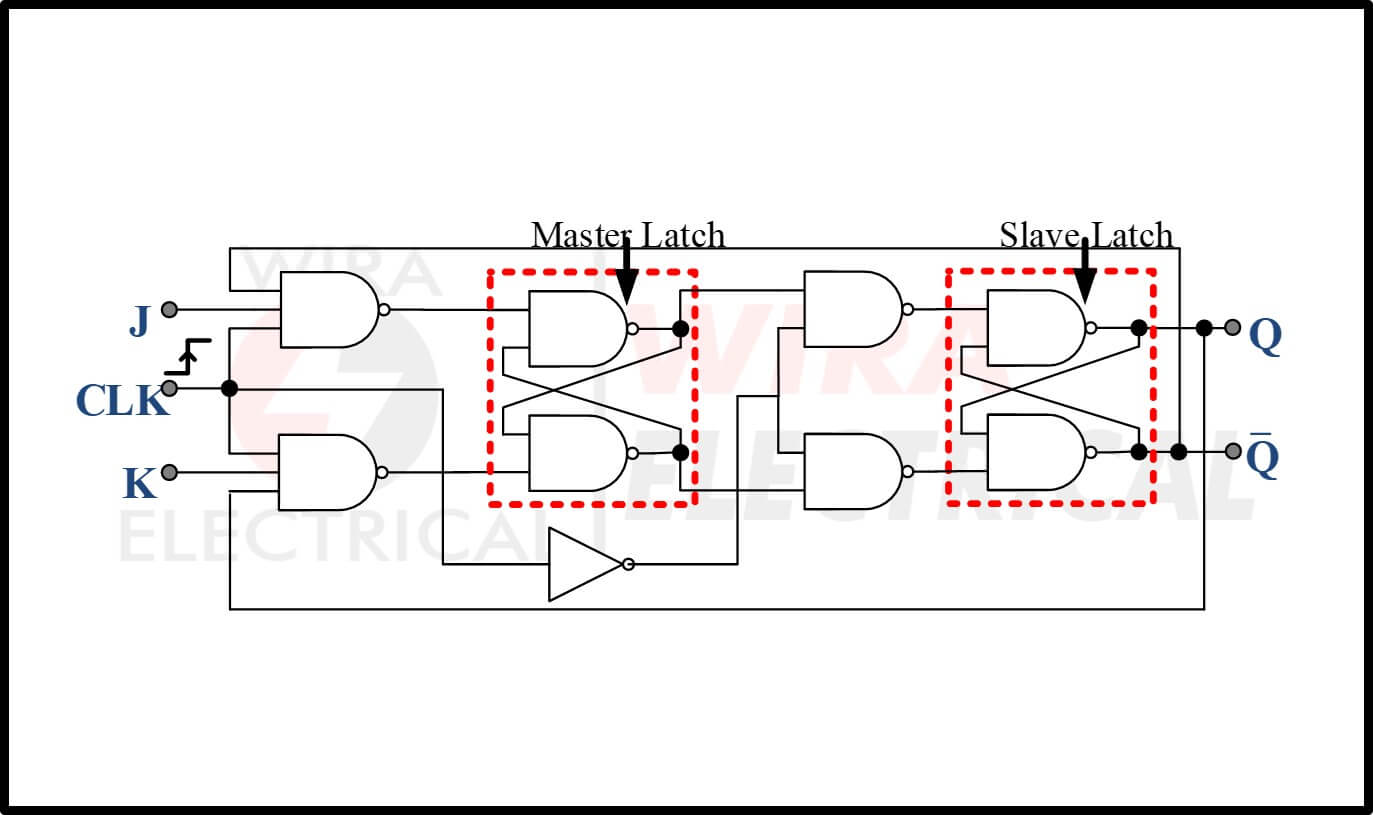

Diagram Rangkaian Master Slave JK Flip Flop dan Tabel Kebenaran

Bila lebar pulsa clock dari flip flop lebih besar daripada delay propagasi flip flop, perubahan output flip flop tidak dapat diandalkan.

Untuk mengatasi masalah ini, kita akan menggunakan pulsa yang dihasilkan oleh flip flop yang dipicu tepi. Pulsa yang dihasilkan oleh bagian detektor tepi dari flip flop akan menjadi pemicu, bukan lebar pulsa yang dihasilkan oleh sinyal input clock.

Fenomena ini disebut sebagai masalah race. Karena delay propagasi biasanya sangat kecil, kemungkinan terjadinya kondisi race cukup tinggi.

Solusi yang paling dikenal untuk menyelesaikan masalah ini adalah dengan menggunakan konfigurasi flip flop slave-master.

Flip-flop JK master-slave

Di atas adalah flip-flop JK master-slave yang dibuat dengan dua flip-flop JK. Ada dua bagian dari jenis flip-flop ini:

- Flip-flop pertama = flip-flop induk

- Flip-flop kedua = flip-flop budak

Input sinyal clock akan dikomplemenkan ke flip flop slave, sedangkan master menerima sinyal input clock secara langsung.

Langkah-langkah operasi flip flop JK master-slave ini adalah:

- Pulsa sinyal clock adalah HIGH ,

- Flip-flop master diaktifkan, tetapi flip-flop slave dinonaktifkan,

- Akibatnya, flip-flop master mampu mengubah status logika outputnya, tetapi flip-flop slave tidak mampu,

- Pulsa sinyal clock adalah LOW,

- Flip-flop master dinonaktifkan, tetapi flip-flop slave diaktifkan,

- Oleh karena itu, status logika flip-flop slave JK berubah sesuai dengan status logika input logika JK.

- Status logika flip-flop master ditransfer ke flip-flop slave, dan flip-flop master yang dinonaktifkan dapat memperoleh input baru tanpa mempengaruhi output.

Dari langkah-langkah di atas, seharusnya jelas bahwa flip-flop master-slave adalah flip-flop yang dipicu pulsa, bukan flip-flop yang dipicu tepi.

Tabel di bawah ini akan menunjukkan kepada kita tabel kebenaran dari flip-flop JK master-slave beserta input LOW PRESET dan CLEAR yang aktif, dan juga input HIGH J dan K yang aktif.

Namun, flip-flop JK master-slave sudah usang. IC modern seperti 74LS, 74AL, 74ALS, 74HC, dan 74HCT tidak memiliki flip-flop master-slave dalam rangkaiannya.

Di bawah ini kita akan mengamati cara kerja master slave dari flip-flop JK menggunakan diagram rangkaiannya.

Amati sepasang flip-flop JK di bawah ini yang membentuk Diagram Rangkaian Flip-Flop JK Master Slave.

Flip-flop Master Slave JK

Kedua sinyal input J, K, dan input clock dihubungkan ke flip-flop R-S “master” yang mampu mengunci input ketika sinyal input clock ‘CLK’ HIGH atau pada status logika “1”.

Sinyal CLK dikomplemenkan sebagai pulsa pewaktu untuk flip-flop R-S “slave”. Ini akan membuat kedua flip-flop bekerja secara bergantian.

Dilihat dari diagram rangkaian di atas, kita dapat menyimpulkan langkah-langkahnya sebagai berikut:

- CLK adalah HIGH atau pada status logika “1”

- Input CLK berada pada status logika “1” untuk “master” dan “0” untuk “slave”

- Input dari “master” terkunci, tetapi output hanya dapat dilihat oleh flip flop “slave”.

- CLK adalah LOW atau pada status logika “0”

- Input CLK berada pada status logika “0” untuk “master” dan “1” untuk “slave”

- Output dari “master” terkunci dan flip flop tidak membaca input apa pun.

- Flip flop “slave” membaca inputnya dari output yang ditransfer dari “master”

Cukup menarik bahwa transisi “LOW ke HIGH” dari sinyal input clock akan memainkan peran besar dalam JK flip flop ini.

‘LOW ke HIGH’: “master” akan mentransfer output-nya. Transisi ini dilengkapi dengan “slave” sebagai ‘HIGH ke LOW’ dan menjadikan input diproses oleh “slave”.

Operasi pengaturan waktu ini menjadikan flip flop ini sebagai edge atau pulse-triggered.

Flip flop menerima status logika input saat CLK HIGH dan mengirimkan data ke output saat sinyal clock dalam kondisi fall-edge.

Oleh karena itu, kita dapat berasumsi bahwa Master-Slave JK flip flop adalah perangkat listrik “Sinkron” karena hanya mengirimkan data pada pengaturan waktu input clock tertentu.

Untuk master slave JK Flip Flop dengan preset dan clear, kita dapat dengan mudah membuatnya dari diagram JK Flip Flop dengan preset dan clear di atas ditambah JK flip flop.

Tabel karakteristik master slave jk flip flop dapat diamati di bawah ini di mana setiap pulsa mempengaruhi pasangan JK flip flop secara berurutan.

Status dalam sel berwarna kuning akan ditransfer ke sel berwarna biru saat CLK dipicu.

Kelemahan JK Flip Flop

Kelemahan utama dan satu-satunya dari flip flop JK telah disebutkan di atas, yaitu Kondisi Race Around. Masalah ini terjadi ketika input J dan K berada dalam status logika “1”.

Kondisi race around terjadi ketika output mengganti output lebih dari satu kali setelah output dikomplemenkan sekali.

Jika masalah ini terjadi, akan sangat sulit untuk memprediksi output berikutnya. Asumsikan jika kita memberi J dan K status logika “1”, pada pulsa clock berikutnya output akan berganti.

Apa yang akan terjadi jika J dan K tetap sama pada status logika “1”?

Output akan berganti sekali lagi dan melanjutkan pola 0101010 dalam skenario nyata. Kita memerlukan flip flop JK master slave untuk mencegah kelemahan ini.

Kita juga memerlukan interval clock yang lebih kecil dari propagasi tunda flip flop. Jika ini tidak tercapai, input tidak akan dapat membaca input sebelum pulsa clock berubah.

IC Flip Flop JK yang Populer

If you are looking for JK flip flop IC, you may consider buying the IC listed below:

- 74LS107 : Dual JK Flip-Flop

- 74LS109 : Dual JK Flip-Flop

- 74LS73 : Dual JK Negative-Edge-Triggered Flip-flop

- 74LS112 : Dual JK Negative-Edge-Triggered Flip-flop

- 74LS76 : Dual JK Positive-Edge-Triggered Flip-Flop

- 74LS114 : Dual JK Negative-Edge-Triggered Flip-Flops DIP-14

- 74LS78 : Dual JK Negative-Edge-Triggered Flip-Flops DIP-14

- NTE74LS76A : TTL Dual JK Flip-Flop with Preset and Clear DIP-16

- 74LS113 : Dual JK Negative-Edge-Triggered Flip-Flops DIP-14

Pertanyaan yang Sering Diajukan

Sekarang kita akan mencoba menjawab pertanyaan yang sering diajukan tentang JK flip flop:

Apa tabel kebenaran JK flip flop?

JK flip flop pada dasarnya adalah versi perbaikan dari R-S flip flop tetapi outputnya tetap sama ketika input J dan K adalah LOW. Operasi logika sekuensial dari JK flip flop ini sama dengan R-S flip flop dengan input logika SET dan RESET yang sama. Satu-satunya perbedaan adalah JK flip flop tidak memiliki kombinasi input terlarang.

Apa cara kerja JK flip flop?

JK flip flop memiliki beberapa input: J, K, S, dan R yang dapat digunakan seperti jenis flip flop lainnya. JK flip flop pada dasarnya adalah versi perbaikan dari R-S flip flop tetapi outputnya tetap sama ketika input J dan K adalah LOW. Flip flop ini adalah kombinasi dari R-S flip flop yang berpagar dan input sinyal yang di-clock.

Apa itu JK flip flop dengan diagram logika?

Karena Q dan Q’ selalu berbeda, kita dapat menggunakannya untuk mengendalikan input. Ketika kedua input J dan K sama dengan logika “1”, flip flop JK akan beralih. Karena Q dan Q’ selalu berbeda, kita dapat menggunakan output untuk mengendalikan input. Jika J dan K keduanya aktif HIGH atau status logika “1”, flip flop JK akan beralih output

Apa kelemahan flip flop JK?

Kelemahan utama dan satu-satunya flip flop JK telah disebutkan di atas, yaitu Kondisi Race Around. Masalah ini terjadi ketika input J dan K berada dalam status logika “1”. Kondisi race around terjadi ketika output beralih output lebih dari satu kali setelah output dikomplemenkan sekali.

Mengapa flip flop JK disebut flip flop universal?

Flip Flop JK dianggap sebagai flip flop universal yang dapat diprogram. Flip flop JK memiliki beberapa input: J, K, S, dan R yang dapat digunakan seperti jenis flip flop lainnya. Flip-flop JK pada dasarnya merupakan versi perbaikan dari flip-flop R-S tetapi outputnya tetap sama ketika input J dan K berkondisi LOW.